CMOS

La Tecnologia CMOS (Complemetary MOS) è un tipo di tecnologia utilizzata in elettronica per la progettazione di componenti digitali utilizzando transistor.

Si fonda su una struttura circuitale costituita dalla serie di una rete di "Pull-Up" ed una di "Pull-Down". La prima s'incarica di replicare correttamente il livello logico alto LL1 mentre alla seconda è destinata la gestione del livello logico basso LL0. La rete di Pull-Up è costituita di soli P-MOS, ovvero quel particolare tipo di transistori MOS che si "accendono" solo se la tensione presente al loro gate è minore della loro tensione di soglia. Inversamente la rete di Pull-Down è costituita di soli N-MOS, ovvero quel particolare tipo di transistori MOS che si accendono solo se la tensione presente al loro gate è maggiore della loro tensione di soglia.

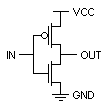

Per poter capire meglio come sia strutturata la tecnologia CMOS può risultare utile osservare una porta logica NOT realizzata con tecnologia CMOS. Si può notare come, nell'eventualità che il segnale d'ingresso sia a LL1, sia il solo N-MOS ad attivarsi portando l'uscita a LL0. Inversamente, con l'ingresso a LL0, è il solo P-MOS ad attivarsi portando l'uscita a LL1. Particolarità di questa porta logica è di avere lo swing logico pieno, cioè pari alla massima tensione applicata, Vcc; inoltre né la rete di pull-up né la rete di pull-down soffre di effetto body. La componentistica realizzata in questa tecnologia è caratterizzata da un consumo di corrente estremamente basso.

Caratteristiche

Forse il principale vantaggio della logica CMOS è di avere una potenza statica dissipata idealmente nulla: questa caratteristica è dovuta alla complementarietà del pull-down (n-Mos) e del pull-up (p-Mos); ossia, quando è acceso il pull-up, è spento il pull-down, e viceversa. Ovviamente, nella realtà c'è una piccola corrente di perdita, trascurabile se il numero dei MOS è relativamente piccolo.

Dimensionando opportunamente i due Mos (simmetrici dal punto di vista funzionale) è possibile avere una curva caratteristica simmetrica, soluzione ottima per avere il margine di immunità ai disturbi (Noise Margin) il più elevato possibile. Il tratto di caratteristica ad alto guadagno è indipendente dal rapporto tra i fattori di forma dei due Mos (ratioless).

È noto che ogni funzione logica binaria può essere espressa in termini di NAND oppure in termini di NOR, che costituiscono quindi gli elementi base per costruire qualsiasi circuito digitale. La realizzazione in tecnologia CMOS della porta logica NAND e della porta logica NOR è:

- NAND: pull-up costituito da due p-Mos in parallelo e pull-down da due n-Mos in serie

- NOR : pull-up costituito da due p-Mos in serie e pull-down da due n-Mos in parallelo

Potenza dinamica dissipata da un CMOS

Si possono identificare due tipi di dissipazioni di potenza dinamica:

- Potenza di cortocircuito

- Potenza associata alla carica/scarica del condensatore

Potenza di cortocircuito

Trascuriamo la capacità parassita e consideriamo un segnale di ingresso che comprenda un fronte di salita e uno di discesa, tenendo presente il ritardo di propagazione ( e sono non nulli). Dall'istante a e da a la corrente non è nulla in quanto sia il PU che il PD sono accesi. Quindi la potenza avrà un valore non nullo in quei punti; ricordiamo che la potenza dinamica è:

Quindi calcoliamo la potenza media:

Facendo l'ipotesi di MOS complementari

Allora

Si viene ad avere

Possiamo conoscere gli estremi di integrazione tramite l'equazione

Sostituendo:

- (Media)Pd = 4Vdd/T [ ∫tr/2 a tr*Vtn/Vdd βn/2(Vi(t)-Vtn)²dt ]

Risolvendo:

Facendo l'ipotesi

Nota: Dipende:

- linearmente dalla durata del fronte di salita (o di discesa)

- dal cubo della tensione di alimentazione

- inversamente dal Periodo (cioè, aumentando la frequenza di lavoro, aumenta la potenza dissipata)

Potenza associata alla carica/scarica del condensatore

Questa volta poniamo e nulli in modo che la e consideriamo il condensatore parassita. Adesso la potenza dissipata sarà quella utilizzata dai MOS per caricare e scaricare il condensatore.

Possiamo identificare 3 parametri:

- = potenza dissipata dal condensatore (in un periodo si sarà caricato e scaricato, quindi avrà assorbito e ceduto la stessa potenza; questo porta ad avere una potenza media dissipata nulla

- - Potenza dissipata dal N-MOS per scaricare il condensatore

- - Potenza dissipata dal P-MOS per caricare il condensatore

Quindi la potenza media dinamica è